Contenido

Introducción

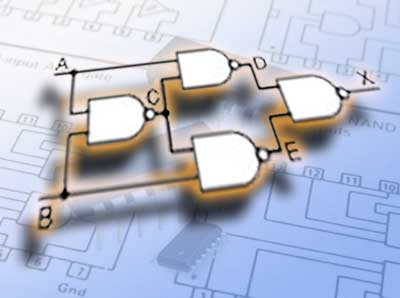

Las puertas lógicas son el corazón de la electrónica digital. Una puerta es un dispositivo electrónico que se utiliza para calcular una función en una señal de dos valores. Las puertas lógicas son el componente básico de los circuitos digitales.

Básicamente, todas las puertas lógicas tienen una salida y dos entradas. Algunas puertas lógicas como la puerta NOT o el inversor tienen solo una entrada y una salida. Las entradas de las puertas lógicas están diseñadas para recibir solo datos binarios (solo bajo 0 alto 1) al recibir la entrada de voltaje.

El bajo nivel lógico representa cero voltios y el nivel lógico alto representa 3 o 5 voltios de suministro positivo.

Podemos conectar cualquier número de compuertas lógicas para diseñar un circuito digital requerido. Prácticamente, implementamos la gran cantidad de puertas lógicas en circuitos integrados, mediante las cuales podemos aprovechar el espacio físico ocupado por la gran cantidad de puertas lógicas. También podemos realizar operaciones complicadas a altas velocidades mediante el uso de circuitos integrados (IC).

Al combinar compuertas lógicas, podemos diseñar muchos circuitos específicos como flip flops, pestillos, multiplexores, registros de desplazamiento, etc.

Niveles lógicos digitales

Un nivel lógico se define como un estado o voltaje específico de una señal. Sabemos que 0 y 1 son los dos estados de puertas lógicas. Los niveles lógicos 0 y 1 se conocen como BAJO y ALTO, respectivamente. En electrónica digital, estos niveles lógicos binarios desempeñan un papel crucial en el almacenamiento de datos, o la transferencia de datos.

Generalmente, estos niveles lógicos se pueden entender como estados ON y OFF. Como dijimos anteriormente, los niveles lógicos se introducen en la puerta lógica mediante el voltaje de suministro. Si el voltaje de suministro a la puerta lógica es 0 voltios, se refiere al nivel lógico bajo o al estado OFF.

De manera similar, si el voltaje de suministro a la puerta lógica es de 5 voltios o 3,3 voltios (para circuitos integrados modernos), se refiere al nivel lógico alto o estado ON. Los fabricantes seguirán el TTL o Transistor-Transistor Logic como nivel de voltaje estándar, mientras se diseñan los circuitos integrados.

¿Qué es Activo Alto y Activo Bajo?

Vemos la entrada activa alta y las clavijas de entrada baja activa en los IC y microcontroladores. ¿Sabes lo que realmente quieren decir? Simplemente nos describen cómo se activa el pin.

Esto significa que el pin activo bajo debe estar conectado a un nivel lógico bajo o a tierra. De la misma manera, el pin alto activo debe estar conectado a un nivel lógico alto o a 5 voltios o 3,3 voltios.

Entendemos esto de una manera simple. Cuando vemos el pin de habilitación CE en un IC de registro de desplazamiento, sin ninguna línea (barra), lo conectamos a la entrada baja activa, es decir, a 0 voltios de tierra. De lo contrario, si vemos el pin de habilitación con una línea como (CE) ̅, lo conectamos a la entrada activa alta, es decir, a 3,3 o 5 voltios de suministro, para habilitar el pin.

Niveles lógicos TTL

El nivel lógico TTL es el nivel lógico estándar para la mayoría de los dispositivos lógicos. TTL significa logica transistor transistor. Los transistores son interruptores controlados eléctricamente. Los niveles de tensión de las familias lógicas son

VOH-mín. nivel de tensión de salida para señal ALTA

VOL-máx. Nivel de voltaje de salida para señal BAJA

VIH-mín. nivel de tensión de entrada de un dispositivo a considerar para ALTA señal

VIL-máx. Nivel de voltaje de entrada de un dispositivo a considerar para la señal BAJA

Si observamos los niveles lógicos TTL, podemos observar que el nivel de alto voltaje mínimo para la salida es de 2.7 voltios. Esto significa que, cuando el dispositivo está funcionando ALTO, el voltaje debe ser de al menos 2,7 voltios.

De manera similar, el nivel mínimo de alto voltaje para la entrada es de 2 voltios. Por lo tanto, los voltajes superiores a 2 voltios se considerarán como lógicos 1, a un dispositivo TTL. Los voltajes entre 0,8 voltios y 2 voltios se conocen como margen de ruido.

De la misma manera, el nivel de voltaje BAJO máximo para la salida es de 0,4 voltios. Esto significa que, cuando el dispositivo está funcionando ALTO, el voltaje debe ser menor que 0,4 voltios. De manera similar, el nivel máximo de bajo voltaje para la entrada es de 0,8 voltios.

Entonces, los voltajes menores de 0 voltios se considerarán como lógicos 0, en un dispositivo TTL. Entonces, cuando el dispositivo lógico recibe voltajes entre 0.8 V y 2 V, el nivel lógico del dispositivo cambiará entre Alto y Bajo. Esta situación se denomina ‘Flotante’.

Otro procedimiento para las tolerancias de entrada y salida del dispositivo TTL es

Niveles lógicos CMOS

Los dispositivos lógicos CMOS también se conocen como dispositivos de 3,3 voltios, porque los dispositivos CMOS tendrán el nivel máximo de voltaje de 3,3 V. Esta es una tecnología avanzada que ejecutará los dispositivos con bajo suministro de energía (3,3 V en lugar de 5 V).

Generalmente utilizamos dispositivos de 5V (compatibles con TTL) para diseñar compuertas lógicas, por lo que estos dispositivos CMOS se utilizan para interactuar con dispositivos TTL. Un dispositivo CMOS puede interactuar con cualquier dispositivo TTL y no requieren ningún componente adicional.

Por ejemplo, el valor mínimo para un alto nivel lógico (1) de un dispositivo CMOS es 2.4 V. Por lo tanto, este dispositivo puede interpretarse con un dispositivo TTL que tiene un voltaje de entrada mínimo para la lógica (V¬IH) 1 como 2 V.

Pero, antes de conectar los dispositivos TTL a CMOS (3.3 V y 5 V), debemos verificar que los dispositivos de 3.3 V son tolerantes a 5 V o no. Debido a que muchos de ellos c dañaran en el chip permanentemente cuando suministremos voltajes superiores a 3.6 V. Podemos usar un circuito divisor de voltaje o cambiadores de nivel lógico para controlar las señales de voltaje de 5 V.

Margen de ruido

El margen de ruido de un nivel lógico se define como la brecha de voltaje entre la tensión máxima baja de entrada alta (VIL max) y la tensión máxima de entrada baja (VIL min) de una puerta lógica. El margen de ruido también se define como la cantidad en que la señal de voltaje excede el nivel de umbral para el mínimo exacto o alto exacto.

Vemos esto con un ejemplo. Cuando un circuito lógico está alternando entre 0 voltios y 1.2 voltios, con cualquier voltaje por debajo de 0.2 voltios se considera BAJO, es decir 0. Y cualquier voltaje superior a 1 voltio se considera ALTO es decir, 1.

Los dispositivos lógicos CMOS tienen mayor nivel de ruido o margen de ruido que los dispositivos lógicos TTL porque su tensión de salida mínima para alta lógica (VOH min) está más cerca de la tensión de alimentación y la tensión máxima de salida para baja lógica (VOL max) es casi 0. Por lo tanto, el nivel de ruido es la máxima cantidad de ruido que un circuito lógico puede soportar.

Si aplicamos un voltaje de cierto nivel de ruido, no sabemos con certeza si el circuito responderá o no. El nivel de ruido es el nivel de voltaje no deseado, causado por interferencia externa como fluctuaciones de voltaje de suministro y otros conductores en el circuito.

El nivel de ruido que un circuito puede tolerar se denomina «Inmunidad al ruido» o «Margen de ruido». Para dispositivos TTL, el rango de tolerancia de los voltajes de salida es mayor que el de los voltajes de entrada.

Puertas lógicas de diodos simples

Los diodos pueden actuar como conmutadores, por lo que se usan en operaciones de lógica digital y conmutación. Para estados de baja y alta impedancia, un diodo funcionará en polarización directa y polarización inversa.

El diodo conducirá solo en una dirección (polarización directa) y permanecerá cerrado en la condición de polarización inversa. Entonces se comporta como un interruptor. Ahora, veamos algunas compuertas lógicas de diodos simples, que se construyen usando solo diodos y resistencias.

Puerta O (OR Gate)

La puerta OR simple diseñada por dos diodos se muestra en la figura a continuación. Las entradas son dadas a este circuito por los dos diodos. En esto, la lógica ALTA (1) está representada por +5 voltios y la lógica BAJA (0) está representada por 0 voltios o masa.

En el circuito de abajo, las dos entradas se dejan desconectadas, por lo que la salida es 0, es decir, lógica baja.

Si cualquiera de las dos entradas está conectada a +5 voltios, entonces el diodo se polariza hacia directamente y conducirá. Por lo tanto, la salida es lógica ALTA, es decir, 1.

Si se conecta una tensión de +5 V a ambas entradas (ambos diodos), estarán en un estado de polarización directa, lo que hace que la salida del circuito O se establezca en ALTA lógica.

El funcionamiento de la puerta OR se da matemáticamente como Z = X + Y, donde Z es la salida de la puerta OR y X, Y son las entradas. La tabla de verdad y el diagrama de lógica y diagrama de circuito para la puerta O lógica se muestran a continuación.

Puerta Y (AND Gate)

La puerta AND simple diseñada por dos diodos se muestra en la figura a continuación. En esto, el voltaje de activación del circuito V se conecta a los dos diodos conectados en paralelo a través de una resistencia, R. Los dos diodos reciben las entradas de este circuito.

En esto, se representa la lógica HIGH (1) en +5 voltios y la lógica BAJA (0) está representada por 0 voltios o tierra.

En el circuito de abajo, las dos entradas no están conectadas, por lo que la salida también es 0, es decir, lógica baja.

Si cualquiera de las dos entradas está conectada a +0 voltios, entonces el diodo se polariza inversamente y no conducirá y hace que la salida lógica sea BAJA, es decir 0.

Si el voltaje de +5 V está conectado a las dos entradas (ambos diodos), ambos diodos estarán en estado de polarización directa, lo que hace que la salida del circuito AND se establezca en logica Alta.

El funcionamiento de de la compuerta Y (AND gate) es matemáticamente dado como Z = X. Y, donde Z es la salida de la puerta AND y X, Y son las entradas. La tabla de verdad y el diagrama lógico y diagrama de circuito para la puerta Y lógica se muestran a continuación.

Circuito logico AND, simbolo lógico y su tabla de verdad

Compuertas lógicas transistorizadas

Al igual que el diodo, el transistor también actúa como interruptor electrónico. Podemos diseñar compuertas lógicas usando transistores también. Echemos un vistazo a las compuertas lógicas hechas por transistor.

Compuerta NO o inversora

La compuerta NOT generalmente se conoce como INVERSOR. Produce la salida inversa exacta a la de entrada dada. Tiene solo una entrada y una salida. La salida de la puerta NO es siempre el complemento de su entrada. Cuando la señal de entrada baja está conectada a la entrada de la puerta NO, la salida será ALTA (lógica 1).

De manera similar, si la señal de entrada alta está conectada a la entrada, entonces la salida será BAJA (lógica 0). La operación NOT se denota con el símbolo de barra ‘-‘. Si la entrada de la puerta NO es X y la salida es Z, entonces la operación de la compuerta NO se da como Z = X ̅, dicha como barra X.

La puerta NOT diseñada mediante el uso de transistores se muestra a continuación. La entrada se da a la base del transistor a través de una resistencia. Y este circuito de transistor es accionado por una tensión de +5 voltios.

Cuando la entrada está conectada a una señal de nivel bajo 0 V, entonces el transistor será polarizado inversamente. Entonces, no fluirá corriente a través de él, por lo tanto, permanece en OFF. Como no hay flujo de corriente a través del transistor, no habrá caída de voltaje en la resistencia. Entonces, la salida corresponderá a +5 voltios haciendo que la lógica de salida sea ALTA.

Pero si +5 V está conectado a la entrada, la tensión de salida será 0. La puerta NO diseñada por el transistor se muestra a continuación.

Hay dos puertas más que se pueden diseñar mediante el uso de transistores, son la puerta NAND y puerta NOR. Estas puertas se llaman «Puertas universales».

Puerta NAND

La puerta NAND tiene la capacidad de realizar 3 operaciones como Y, O y NO. Esta puerta es una combinación de NOT y la puerta AND. La salida de puerta NAND es igual a la inversa de la puerta AND.

La puerta NAND tiene dos entradas X e Y, y una única salida Z. Las entradas se aplican a los diodos que están conectados al transistor. El circuito de compuerta NAND es accionado por +5 voltios.

Cuando ambas entradas están conectadas a una fuente de voltaje de 5 V, ambos diodos D1 y D2 están en estado OFF. Entonces el transistor Q1 puede conducir desde la tensión de alimentación a través de la resistencia. Entonces el transistor está en estado ON y la tensión de salida Vce (Sat) se convierte en 0.

De manera similar, cuando se aplica un voltaje de nivel bajo a las entradas, es decir 0 V, el transistor estará APAGADO y el voltaje de salida se convierte en +5 V. Matemáticamente, la compuerta NAND se representa como Z = (XY) ̅.

Entonces, la salida de la compuerta NAND se vuelve BAJA solo cuando ambas entradas son altas. Se vuelve ALTO para cualquier otra combinación de entradas. La tabla de verdad, el símbolo lógico y los diagramas de circuito del transistor de la compuerta NAND se muestran a continuación.

Compuerta NOR

La compuerta NOR es la combinación de la compuerta NOT y la compuerta OR. La salida de la puerta NOR es igual a la inversa de la puerta OR. La puerta NOR tiene dos entradas X e Y, y una única salida Z.

La puerta NOR diseñada con transistor tiene dos transistores npn con la tensión de alimentación o +5 voltios.

Cuando ambas entradas de la puerta NOR están conectadas a 0 voltios, entonces los transistores Q1 y Q2 están en estado apagado. De modo que no fluye corriente a través de la resistencia y no hay caída de tensión en la resistencia. Entonces la tensión de salida es igual a la tensión de alimentación +5 voltios, es decir, nivel lógico ALTO.

Si cualquiera de las entradas está conectada a +5 V, entonces los transistores estarán en estado ON. Entonces la caída de voltaje sería alta. Por tanto, la tensión de salida del circuito será 0 V, es decir, igual a la tensión de tierra.

Matemáticamente, la puerta NOR se representa como Z = (X + Y) ̅.

Así que la salida de la compuerta NAND pasa a ser ALTA solo cuando ambas entradas son bajas. Se vuelve BAJO para cualquier otra combinación de entradas. La tabla de verdad, el símbolo lógico y los diagramas de circuito del transistor de la puerta NOR se muestran a continuación.

Circuitos Integrador de la serie 74

Los IC series 7400 se introducen alrededor de 1960. Aunque se usan muchos otros circuitos integrados para puertas lógicas, los circuitos integrados de la familia 7400 TTL se han vuelto los más populares debido a su esquema de numeración y estándares simples. Algunas de las especificaciones y características principales se dan a continuación.

Los circuitos integrados de la serie 74 se fabrican utilizando tecnología de transistor bipolar, por lo que se denominan circuitos integrados de la familia TTL. (TTL significa Transistor-Transistor Logic). Los circuitos integrados 7400 funcionarán con suministro de +5 voltios y este se convirtió en el nivel de voltaje estándar de los circuitos lógicos durante muchos años, hasta la evolución de la tecnología CMOS.

Estas son las series IC ampliamente utilizadas para el diseño decircuitos lógicos. Anteriormente a estos circuitos integrados de la serie 7400, tenemos chips de serie TTL. Motorola Company lanzó una familia lógica con el nombre MTTL, que significa Transistor de Motorola-Logística Transistor.

Otros investigadores y fabricantes como Signetics, Fairchild y National Semiconductor también lanzaron algunas otras series de circuitos integrados.

Hay varias familias de IC numeradas como 74xx00. Las letras en el lugar de xx indicarán el tipo de IC y las especificaciones. Los diferentes tipos de series IC son 74LS00, 74HC00 y 74HCT00, etc. Dejemos las especificaciones y los propósitos de cada serie IC.

Serie 74LS

Esta es la familia Schottky de baja potencia que usa circuitos TTL. Son rápidos en las operaciones pero consumen más energía que otras familias lógicas.

Serie 74HC

Esta serie es familia CMOS de ALTA velocidad. Estos IC tienen la combinación de características de baja potencia de la serie 4000 y la velocidad de la serie 74LS.

Serie 74HCT

Esta es una versión muy especial de la familia 74HC. Tiene entradas 74LS TTL compatibles. Por lo tanto, se puede interconectar fácilmente con la serie 74LS. La familia 74HCT se usa como reemplazo de la serie 74LS, ya que son requisitos de baja potencia.

La desventaja de la serie 74HCT es que son menos inmunes al ruido, es decir, tienen menos tolerancia al ruido.

Los circuitos CMOS utilizados en las series 74HC y 74HCT debido a su sensibilidad estática. Esto significa que si tocamos cualquier pin del IC mientras se está cargando, dañará el IC.

Los prefijos para los circuitos integrados de la familia TTL y CMOS se enumeran a continuación.

Algunos IC más utilizados para el diseño de compuertas lógicas se dan a continuación

Compuertas cuadruples de 2 entradas

- 74LS00-Entrada NAND Quad de 2 entradas

- 74LS01-Entrada NAND Quad de 2 entradas, salidas de colector abierto

- 74LS02-Puerta NOR de dos entradas Quad

- 74LS03-Entrada NAND Quad de 2 entradas con salidas de colector abierto

- 74LS08-Quad AND-Input AND Gate

- 74LS09-Entrada AND de cuádruple entrada con salidas de colector abierto

- 74LS32-Quad de 2 entradas OR Gate

- 74LS132-Entrada NAND Quad de 2 entradas con entradas de activación Schmitt

- 74LS37, 74LS32, 74LS28-Quad 2-InpuT NOR Gates

- 74LS26-Quad 2-InpuT NAND Gate, OC (15V)

- 74LS28-Quad 2-InpuT NAND Gate con OC (15V)

- 74LS33-Puerta NOR Quad Quad-InpuT, salidas de colector abierto

- 74LS38-Puerta NOR Quad Quad-InpuT, salidas de colector abierto

- 74LS38-Entrada NAND Quad de 2 entradas, salidas de colector abierto

Puertas triples de 3 entradas

- 74 LS 10-NAND Triple 3-inpuT

- 74 LS 11-Triple de 3 entradas Y

- 74 LS 12-NAND Triple 3-inpuT con salidas de colector abierto

- 74 LS 27-Triple 3-inpuT NOR

- 74LS15-Puertas triples de 3 entradas y compuerta, salidas de colector abiertas

Compuertas dobles de 4 entradas

- 74LS13-Disparadores dobles Schmitt NAND 4-InpuT

- 74 LS 20-NAND doble de 4 entradas

- 74 LS 21-dual 4-inpuT Y, salidas de colector abierto

- 74LS22-Puertas NAND Gate dobles de 4 entradas, salidas de colector abierto

- 74LS40-Puertas NAND duales de 4 entradas

- 74LS30-Puerta NAND de 8 entradas

Puertas hexagonales NO

- 74 LS 04-hex NO

- 74 LS 05-hex NO con salidas de colector abiertas

- 74 LS 14-hex NO con las entradas de Schmitt Trigger

- 74LS19-NAND Schmitt Trigger, Totem Pole Output

- 74LS23-2x Cuatro entradas NOR con Strobe

- 74LS25-2x Cuatro entradas NOR con Strobe

- 74LS30-8-InpuT NAND Gate

- 74LS39-4x dos entradas NAND, colector abierto